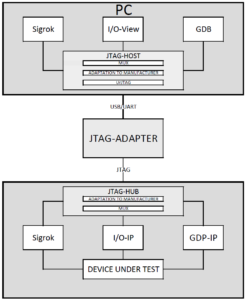

We clearly distinguish, when talking about this this project (you can find an overview of the whole project below), the LogicAnalyser and I/O_View. The LogicAnalyser allows you to show a signal as a function of time, whereas I/O_View in turn is able to set and read out different flip-flop states. The only thing that they both need and have in common is the jtag-interface. This common property is a great advantage because like this both projects can be used simultaneously.

I/O_View

I/O_View consist of a hardware description and a software component. The hardware description includes a controller-component and an escaping-component. We have defined five commands to control the hardware description I/O_View.

reset => 0xEE

escaping => 0x55

read out- and inputwidth => 0xAB

write output => 0xBB

read input => 0xAA

But these commands are only of interest to you, if you do not use our software component.

If you want to readout or set a flip-flop state, you first have to include the IoViewTop component into your project. Afterwards you have to connect the signals probe_inputs or probe_outputs of the IoView component with the corresponding flip-flops.

Then you can start the software program IOView. On IOView you first have to connect the software program to the Jtag_host. To do so, you need to know the IP address of your computer and the port number of IOView. The port number is defined in the Jtag_Hub component. If you didn’t alter it, the port number should already be set to 4243. Before connecting IOView to Jtag_host don’t forget to start the Jtag_host.

LogicAnalyser/Pulseview

The project LogicAnalyser/Pulseview is larger than the project IOView. Still it has the same basic components: a hardware description and a software component.

The hardware description is made up of the components LogicAnalyserMemory, LogicAnalyserTrigger, LogicAnalyserController and IpdbgEscaping. All the names should be self-explanatory.

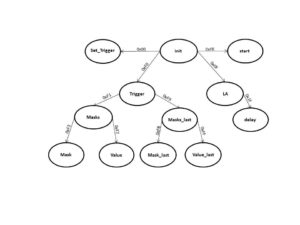

The control of the LogicAnalyser is more complicated than the control of IOView because we also want to be able to set the trigger terms. To facilitate your control of the LogicAnalyser we have designed the following graphical state representation.

Absatz fehlt noch!

reset => 0xEE

escaping => 0x55

read inputwidth => 0xAA

get ID => 0xBB

start the LogicAnalyser => 0xFE

But this information is only of interest for you, if you don’t use the software Pulseview.

To use the LogicAnalyser you have to include the LogicAnalyserTop in your project and connect the probe input signal to the corresponding flip-flop of your project.

The software component Pulseview is a part of our project, that we didn’t develop ourselves. Pulseview is a cross-platform Qt-based GUI for the sigrok software, suitable for test and measurement equipment such as logic analyzers, oscilloscopes, MSOs, and more. We only implemented our LogicAnalyser in Sigrok to be able to use Pulseview. We decided to use Pulseview because the projects fitted together nicely and like that we could profit from the work, that has already been done.

Information about Sigrok and Pulseview:

To use Pulseview you need to know the IP-Address and the port of the LogicAnalyser. The port number is defined in the Jtag_Hub component. If you didn’t alter it, the port number should already be set to 4243. Before you connect the LogicAnalyser with Jtag_host don’t forget to start the Jtag_host.

JTAG-HOST / JTAG-HUB

The Component JTAG-HOST receives the data from Sigrok and I/O-View over TCP and prepares the data before it is sent over the jtag-adapter to the FPGA. We are using the urjtag library to make sure that we can use different jtag-adapters. http://urjtag.org/

If you want to use a different jtag-adapter than the Ft2232 you have to change some statements. How this is done is described here: http://www.ipdbg.org/?page_id=63

The JTAG-HUB consists of two parts. With one part can you set with which technology you are working and the other part is the multiplexer. So far this project has been tested on Xilinx Spartan3 on Lattice ECP2 and on ICE40.

The instructions for setting which technology you want to use you can find here: http://www.ipdbg.org/?page_id=66

The LA-IP and I/O-View receive the prepared data from the JTAG-HUB and send the states of the flip-flops back to the corresponding software-program.